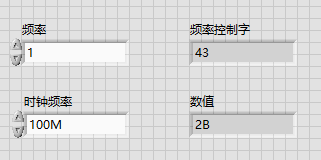

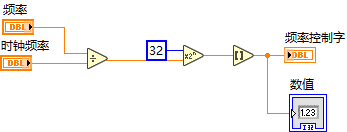

首先需要已知时钟频率是多少,它的底层是基于DDS的原理去实现的。它的计算方法可以见这个LabVIEW小程序;

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2023/04/06 09:24:24

// Design Name:

// Module Name: clk_file

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module clk_file(

clk ,

rst ,

FREQUENCY_CLK ,

clk_gens1 ,

clk_gens1_p ,

clk_gens1_n ,

phase

);

//////////////////////////////////////////////////////////////////////////////////

input clk ;

input rst ;

input [31:0] FREQUENCY_CLK;

output clk_gens1 ;

output clk_gens1_p ;

output clk_gens1_n ;

output [11:0] phase;

//////////////////////////////////////////////////////////////////////////////////

reg [31:0] cnts;

reg [11:0] phase;

always @ (posedge clk or posedge rst)

begin

if(rst)

begin

cnts<=32'd0;

end

else

begin

cnts<=cnts + FREQUENCY_CLK;

end

end

always @ (posedge clk or posedge rst)

begin

if(rst)

begin

phase<=12'd0;

end

else

begin

phase<=cnts[31:20];

end

end

//////////////////////////////////////////////////////////////////////////////////

reg clk_gens1_use;

always @ (posedge clk or posedge rst)

begin

if(rst)

begin

clk_gens1_use<=0;

end

else

begin

clk_gens1_use<=cnts[31];

end

end

//////////////////////////////////////////////////////////////////////////////////

reg clk_gens1_p;

always @ (posedge clk or posedge rst)

begin

if(rst)

begin

clk_gens1_p<=0;

end

else if((cnts[31]==1'b1)&&(clk_gens1_use==1'b0))//posedge

begin

clk_gens1_p<=1'b1;

end

else

begin

clk_gens1_p<=1'b0;

end

end

reg clk_gens1_n;

always @ (posedge clk or posedge rst)

begin

if(rst)

begin

clk_gens1_n<=0;

end

else if((cnts[31]==1'b0)&&(clk_gens1_use==1'b1))//negedge

begin

clk_gens1_n<=1'b1;

end

else

begin

clk_gens1_n<=1'b0;

end

end

//////////////////////////////////////////////////////////////////////////////////

reg clk_gens1;

always @ (posedge clk or posedge rst)

begin

if(rst)

begin

clk_gens1<=0;

end

else

begin

clk_gens1<=clk_gens1_use;

end

end

//////////////////////////////////////////////////////////////////////////////////

endmodule

调用模块:生成1Hz的时钟信号

wire fll_clk_rate; // 100M的时钟

clk_file DATA_CLK(

.clk (clk),

.rst (rst),

.FREQUENCY_CLK (32'd43), // 1@110M

.clk_gens1 (),

.clk_gens1_p (fll_clk_rate),

.clk_gens1_n (),

.phase ()

);